VLBI 系统由天线、接收机、本振系统、数据采集终端、数据记录设备和数据相关处理机等部分组成。其中数据采集终端承担中频分配、下变频、数据编码和数据记录等任务,是VLBI台站的重要设备。随着数字技术的进步,使 VLBI的实时性、更高精度等发展目标成为可能,为此对数据终端提出了新的要求:(1)对中频模拟信号采样得到数字信号;2)每路中频信号的带宽至 512MHz 或更宽;(3)通过数字信号处理的办法实现变频。VLBI 技术就是把多个望远镜联合起来,通过干涉的办法获得超大望远镜的观测效果。基线两端的射电望远镜各自以独立的时间标准(氢原子钟等),同时接收同一个射电源的信号,经过数据采集系统后,记录于磁盘并将两磁盘的记录一起送入处理机作相关处理, 求出相同信号到达基线两端的时刻之差 (简称时延)和相对应的时延变化率(简称时延率),以及干涉条纹的相关幅度等观测量[9]。

通过高速A/D对中频信号采样后,在FPGA 内采用数字信号处理的办法实现数据采集终端是目前的主流发展方向。目前国际上进行相关研究的有欧洲EVN 的DBBC(Digital Base-Band Converter)、美国的 DBE(Digital Backend)、日本的 ADS3000 系列和中国的CDAS。

CDAS设备要求从带宽为512MHz的中频,在不同频点上按要求提取窄带信号,并搬移至基带。CDAS 主要由三部分组成:模拟射频部分、数字部分和输出接口部分。

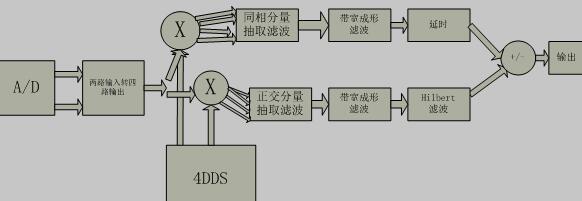

CDAS 数字算法部分的主要功能是以高速A/D采样后的8bits数字信号作为输入,经过DDS混频和低通滤波实现下变频的功能,输出为64MHz时钟的具有一定带宽的基带信号。

图1.1 算法部分框图

CDAS作为数据采集系统的主要部分,将观测频段的信号下变频后,以基带的形式经过编码后送到数据记录系统。CDAS主要由三部分组成:模拟射频部分、数字部分和输出接口部分。模拟射频部分主要有两大功能:利用氢钟的5MHz信号产生1024MHz 高精度高稳定的时钟信号、对接收机输出的宽带信号进行抗混叠滤波产生512M带宽的中频信号,并且对四路中频信号进行自动增益控制使之处于最佳状态以利A/D采样。数字部分由一台工业控制计算机和数字信号处理板组成。控制计算机是基于PCI总线架构的,具有以下功能:接收FS计算机的指令设置通道的频率、带宽等;接收通道零基线相关的计算结果;提取相位校正信号和检测系统状态。信号处理板是CDAS的重要组成部分,实现信号从中频到基带的转换。输出接口部分由数据综合板和接口板组成。数据综合板负责输出数据的模式选择(1/2/4bits)、输出通道的选择以及电平转换。接口板提供MK4 或者VSI接口,将数据送到记录设备(如MK5A、Mk5B)[9]。图1.2为CDAS框图。

图 1.2 CDAS框图

上海天文台VLBI实验室准备对探月三期台站设备进行升级改造,深空探测中希望对卫星用窄带观测,而对射电源用宽带观测,为满足该要求,拟采用先进行混频,将各频点信号搬至低频段,再用滤波器进行滤波。混频中利用直接数字式频率合成器(DDS: Direct Digital Synthesizer)作为本振,但是目前常用的DDS的频率精度并不能满足工程需求,设计新型的混合十进制DDS已经迫在眉睫。传统的DDS计算精度是有误差的,而混合十进制DDS的计算精度是一个整数,传统的DDS的相位不连续,出来的相位不是设定的初相,因为寄存器没有清零,设计一个能够可以在DDS运行中随时切换其频率和相位的混频DDS迫在眉睫。

1.2论文期间的主要工作

查阅相关资料,了解甚长基线干涉测量技术(VLBI)技术,掌握DDS的基本原理,学会使用Xilinx ISE,能够运用Xilinx ISE软件中的VHDL进行构建工程,知道混合十进制DDS的算法,熟练的运用VHDL硬件编程语言进行程序的编写,硬件描述语言 VHDL ( ( Very High Speed Integrated Circuit ) Hardware Description Language )是EDA的关键技术之一, VHDL是作为电子设计主流硬件的描述语言, 在电子设计自动化中扮演着重要的角色, 成为数字系统设计领域最佳的硬件描述语言, 它是EDA技术研究的重点之一。VHDL的特性是它和设计平台、具体的硬件电路无关,而且它拥有极好的电路系统和行为的描述的能力,可以从多个层次对数字系统进行描述、建模和简化硬件设计任务,大大的增加了设计的可靠性和效率。VHDL解决了传统系统设计的效率低、不可靠、成本高的弊端,使系统可以随时的进行仿真模拟。用VHDL进行设计,设计者可以不用具体的了解硬件的结构,也不用管最终设计实现的目标器件是什么,可以进行单独的设计。