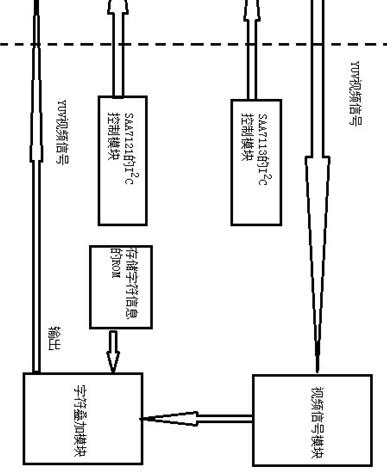

图2.1 视频字符叠加原理图

3 系统软件具体设计

本系统以由Altera公司设计开发的一种可编程逻辑设计环境Quartus 11作为软件开发环境,它具有直观易用的接口,强大的设计能力,友好的用户界面和丰富的应用解决方案等优点,因此深受广大软件开发人员的喜爱。

Quartus II 是一种可以使用AHDL(Altera Hardware Description Language),原理图,VHDL和Verilog HDL等设计输入形式的综合性PLD开发软件,同时该软件拥有比如matlab,signal2等配套的综合仿真软件,对于实现系统整个工程方案从设计到硬件调试的验证非常有利。Quartus2能与第三方综合仿真软件完美兼容,这使得设计用户在设计流程的不同阶段选择相应的设计工具,有利于缩短设计周期。Quartus II还支持Altera公司设计产品中的IP核,开发者可以免于设计复杂的门电路,而是通过从LPM/MegaFunction宏功能模块库中调用软件环境中的已有的模块来进行设计,充分缩短了设计耗时提高了设计速度。

本课题的系统软件设计包括图像处理模块即视频接收模块,I2C总线控制模块分为SAA7113和SAA7121的两个控制模块,存储字符信息的ROM模块,字符叠加模块以及构成ROM中的初始化数据文件格式为mif。

如图2.1中,I2C控制模块功能是实现对视频编解码芯片的初始化,图像处理模块用来将接收到的视频信号中的有效视频信号与控制信号分离出来,字符叠加模块接收前一个模块的信号并根据他们将字符信息在特定位置与经处理的视频信号进行叠加,完成系统功能。

3.1 I2C 控制总线的设计

本系统通过设计出对I2C总线的模拟模块来实现对视频编解码芯片即SAA7121,SAA7113的内部寄存器的初始化配置,以使它们实现对数字视频信号的符合需求的处理,输出的经处理的视频信号为后续的模块所用。首先介绍一下I2C总线。

3.1.1 I2C总线

I2C总 线是一种由时钟线SCL和数 据 线SDA组 成的具有较高 的数据速率、控制方式简单和I/O资源利用率 高等优点的将外来设备和系统内部的控制器运用两线式同步串行方式连接在一起的总线结构,作为微电子通信控制领域的一种总线标准而被广泛采用。I2C总线工作方式是一种可发送与接收数据的半双工同的通信方式。时钟线SCL和数据线SDA都是为双向通信线路的I/O端口,二者连接到正的电源电压由电流源或上拉电阻提供。当SCL和SDA保持在高电平表明此时I2C总线处于空闲状态。I2C总线由主器件控制下能达到3.4Mbit/s的高速模式,达到标准模式时,数据传输速率不超过100Kbit/s,快速模式在400Kbit/s左右。

I2C总线通信协议规定,在数据传输过程中起始信号与停止信号必须由主器件提供,而从器件会在接受数据之后提供用于反馈数据传输状态的应答信号。

图3.1 I2C通信协议时序

从图3.1中可知,在总线开始工作时要求SDA信号由高到低进行电平跳变,此时SCL处于高电平,数据信号开始传输;在总线结束工作时SDA信号由低到高进行电平跳变,此时SCL处于高电平,表明数据传输结束。由于输出数据SDA上的数据会在时钟信号SCL处于高电平时进行传输,这就要求在SCL处于高电平时SDA上的数据必须保持稳定,另外数据线上的数据只能在时钟线处于低电平的时侯才能进行改变,这一点需要特别注意。此外I2C总线虽然没有限制每次可传输的字节数,但是要求每次必须发送8bit的数据信息,否则传输过程不能正确进行,发生传输错误 。